なぜRISC-Vを採用するのか?

半導体業界は大きな転換期を迎えている。ムーアの法則の限界が見え始め、チップの設計思想も単一の高性能コアから、複数の異なる種類のプロセッサを組み合わせるヘテロジニアス(異種混合)アーキテクチャへと移行している。この変化の中で、オープンソースのISA(命令セットアーキテクチャ)であるRISC-Vへの注目が急速に高まっている。

また、従来のISAが抱える技術的な制約や、ライセンスモデルの限界は、今後の半導体設計において大きな障壁となりうる。一方、RISC-Vはこれらの問題を解決し、将来の技術発展を加速させる可能性を秘めている。

本記事を執筆する動機は、業務でRISC-Vを使用する中で、その採用がもたらす技術的・経済的なメリットを明確に言語化したいと考えたためである。そのため、この記事では、RISC-Vを採用すべき理由について、以下の2つの観点から論じる:

- RISC-Vは過去のISAの失敗から学び、技術的に優れた設計を実現している。

- 近年の半導体業界ではヘテロジニアスなチップが増加しており、オープンソースISAの重要性が高まっている。

特に後者の点が、今後の半導体業界において決定的な要因になると考えている。

1. RISC-Vの技術的優位性

従来のISAは、拡張性の制約や設計の複雑化といった課題を抱えてきたが、RISC-Vはこれらの問題を克服し、シンプルで柔軟な設計を実現している。

“RISC-V is an open source instruction set architecture (ISA). It is designed to be simple, modular, and extensible, providing a foundation for building a wide range of processors and systems.”

— Wind River Software

ここでは、x86とMIPSのISAの設計上の問題点を取り上げ、それに対するRISC-Vのアプローチを説明する。

x86: CISCの複雑性によるデコードのボトルネック

x86は、Intelが開発した命令セット・アーキテクチャ(ISA)のファミリーであり、パーソナルコンピューター、サーバー、組み込み機器などの幅広いプロセッサに採用されている。

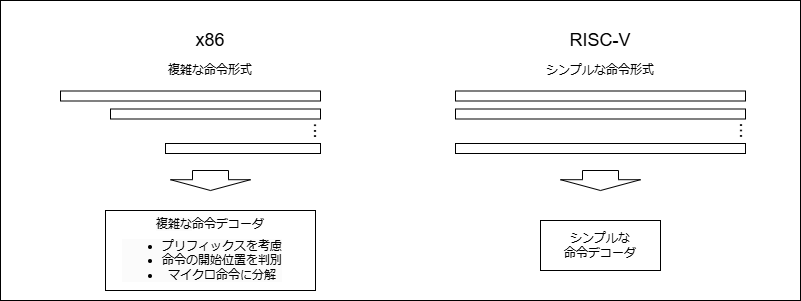

長年の拡張により、x86の命令セットは膨大になり、命令デコード(機械語を実際の処理に変換する作業)の処理が極めて複雑化した。特に、可変長命令を採用しているため、命令の長さが1バイトから15バイトまで変動し、並列デコードが困難になる。これにより、プロセッサは常に正確に命令の開始位置を特定する必要がある。

さらに、一部のx86命令は単一の命令として記述されていても、内部的には複数のマイクロオペレーション(μops:プロセッサが実際に実行する基本的な操作単位)に分解される。この変換処理がデコードの負荷を増大させ、性能の低下を招く要因となる。また、x86の命令デコードは、特定の命令に付加されるプリフィックス(命令の動作を修飾する追加情報)の影響を受けることが多く、デコーダの設計をさらに複雑にしている。

図1は、x86とRISC-Vの命令デコード処理の違いを示している。x86では可変長命令と複雑なデコード処理が必要なため、多段のデコーダと変換ロジックが必要となる。一方、RISC-Vは固定長の単純な命令形式を採用しており、デコード処理が大幅に簡素化されている。

その結果、x86プロセッサでは、複雑なISAがデコード性能のボトルネックとなる。この問題を緩和するために、最新のx86プロセッサにはμopキャッシュやトレースキャッシュといった補助機構が導入されている。しかし、これらの対策は根本的な解決には至らず、デコードを高速化するために多くのトランジスタを消費する複雑なデコーダーユニットが必要とされる。

一方、RISC-Vではこれらの補助機構自体が不要である。RISC-Vは固定長32ビット命令を採用しており、命令デコードがシンプルで高速に処理できるよう設計されている。また、ほぼすべての命令が1:1の比率で実行ユニットに送られるため、マイクロオペレーションへの変換が不要である。これにより、ハードウェアの設計が簡素化され、結果として高クロックでの動作が実現しやすくなっている。

MIPS: 遅延分岐の問題

MIPSはx86とは異なり、RISCアーキテクチャ(命令セットを単純化し、高速実行を目指す設計思想)として誕生し、シンプルな設計思想に基づいて構築された。しかし、初期のパイプライン設計を簡略化するために遅延分岐という手法を採用したことが、後のプロセッサ設計において問題となった。

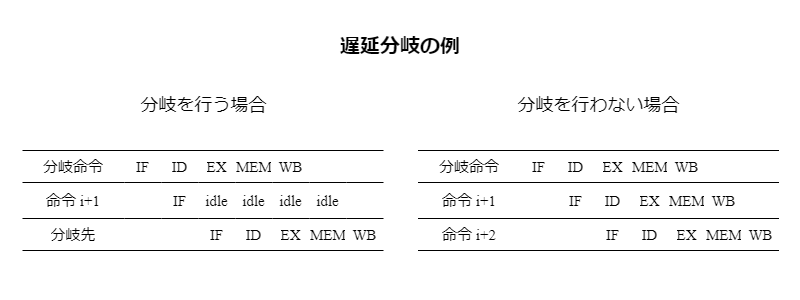

MIPSの遅延分岐は、分岐命令の次の命令を、分岐結果にかかわらず必ず1サイクル実行するという設計である。これにより、分岐によるパイプライン(命令を複数のステージに分けて並列処理する仕組み)のストール(処理の一時停止)を回避し、ハードウェアの単純化を実現できる。

図2は、遅延分岐を採用した場合の命令パイプラインの動作を示している。分岐命令の直後の命令 i+1(Delay Slot)は、分岐の成否に関係なく必ず実行される。これにより、分岐命令がパイプラインの実行段階に達して分岐条件が評価されている間も、後続の命令(Delay Slot内の命令)がフェッチされ、デコードされ続けることができる。通常のパイプラインでは分岐先が確定するまで次の命令をフェッチできないためストールが発生するが、遅延分岐ではこの待ち時間を有効活用できる。つまり、分岐判定結果を待つ間もパイプラインが空になることなく処理を継続できるため、パイプラインストールを回避できるのである。しかし、この設計には実際にはさまざまな問題を引き起こす。

まず、コンパイラの最適化が難しくなる。分岐命令の直後に実行される命令(遅延スロットの命令)は、分岐命令の前後の命令と独立していなければならない。しかし、実際のプログラムでは独立した命令を都合よく配置できるとは限らず、適切な命令が見つからない場合はNOP(No Operation:何もしない命令)を挿入する必要がある。NOPは何もしないにもかかわらず、1サイクルを消費して、また命令キャッシュのスペースを占有するため、結果としてパフォーマンスの低下を招く可能性がある。

さらに、近年の高性能プロセッサでは、分岐予測技術(次の分岐先を予測して先行実行する技術)の発展により、分岐命令の影響を最小限に抑えることが可能となった。そのため、遅延分岐を前提とした設計はかえって不利となり、特にスーパースカラ実行(複数の命令を同時に実行する技術)やアウト・オブ・オーダー実行(命令の依存関係を考慮しつつ、実行順序を動的に変更する技術)を採用するプロセッサでは、命令の流れが複雑になりすぎる要因となってしまった。

RISC-Vは、遅延分岐を採用せず、最新の分岐予測技術を前提とした設計を行っている。これにより、命令の流れがよりシンプルになり、高速な実行が可能となる。

2. RISC-Vがオープンソースであることの重要性

これまで見てきたように、RISC-Vは技術的な設計において優れた選択をしてきた。x86の複雑なデコード処理やMIPSの遅延分岐といった過去のアーキテクチャが抱える問題を回避し、シンプルで効率的な設計を実現している。もちろん、RISC-VにはモジュラーなISAの設計や、ゼロレジスタの使い方など、上記で紹介した点以外の技術的優位性が数多く存在する。

しかし、RISC-Vの真の革新性は、その技術的な設計だけでなく、オープンソースのISAというビジネスモデルにある。半導体業界のパラダイムシフトが進む中、単に技術的に優れているだけでなく、オープンで柔軟なエコシステムを構築できることが、次世代ISAにとって不可欠な要素となっている。

“RISC-V is a free and open ISA enabling a new era of processor innovation through open standard collaboration.”

RISC-V International

ISAのビジネスモデル比較

従来のISAとRISC-Vのビジネスモデルを比較すると、そのオープンソースであることの優位性がより明確になる。

| ISA | チップ 提供企業の数 |

ライセンス | 商用コアIPの提供 | 独自命令の追加 | オープンソース のコアIP |

|---|---|---|---|---|---|

| x86 | 3社 (Intel, AMD, VIA) |

非公開 (相互ライセンス契約) |

なし | 不可 | なし |

| ARM | 500社以上 | 年間数億円~ | ARM社のみ | 制限付き | なし |

| RISC-V | 200社以上 (急増中) |

無料 | SiFive, Andes等 多数 |

完全に可能 | BOOM, Rocket等 多数 |

x86アーキテクチャを採用したチップは、Intel、AMD、VIAの3社のみが提供している。これは、x86のライセンスが非公開で、これら3社間の複雑な相互ライセンス契約に基づいているためである。さらに、x86アーキテクチャを独自に設計することはできず、既存のコアを利用するしかない。独自命令の追加も不可であり、オープンソースのCPUも存在しないため、柔軟性に欠ける。

ARMは500社以上のベンダーがチップを提供しているが、独自のCPU設計には年間数億円規模のライセンス費用が必要である。2024年のQualcommとARMの訴訟問題にも見られるように、ライセンス契約には厳しい制約がある。さらに、チップに組み込めるCPUはARM社が提供するものに限られ、カスタマイズの自由度が制限される。

これに対し、RISC-Vは特定の企業に依存しないオープンな標準であり、すでに200社以上のベンダーがRISC-V対応のチップを提供している(2025年時点)。アーキテクチャのライセンスは完全に無料であり、企業や研究機関が自由にRISC-Vベースの設計を行うことができる。商用のRISC-VコアIPも、SiFive、Andes Technology、Codasip、CloudBearなど、複数のベンダーが提供しており、用途に応じて最適なコアを選択できる。さらに、RISC-Vでは独自命令の追加が完全に自由であり、用途に応じた最適化ができるため、性能向上や消費電力の最適化に大きく寄与する。

また、BOOM(Berkeley Out-of-Order Machine)やRocket Coreなど、多くの高品質なオープンソースRISC-V CPUが開発されており、誰でも自由に利用・改良できる点も大きな強みである。これにより、新規参入企業でも、既存の設計資産を活用しながら、独自の最適化や機能追加を行うことが可能となる。

モダンSoCにおけるISAの多様化とオープンISAの必要性

現代のシステムオンチップ(SoC)は急速にヘテロジニアス(異種混合)化が進んでいる。最新のスマートフォン向けSoCには、ARM Cortex-A78のような高性能コア、Cortex-A55の省電力コア、Cortex-M33のリアルタイム処理用マイクロコントローラが共存している。さらに、Mali-G78などのGPU、画像処理用ISP、機械学習加速用NPU、音声処理用DSP、セキュリティ機能を担うTEEなど、様々な専用プロセッサが単一チップ上に集積されている。これらは全て異なるアーキテクチャやISAを持つため、ソフトウェア開発者は複数の開発環境やツールチェーンを扱う必要があり、大きな負担となっている。

このような状況が生じた主な要因は三つある。まず、AI処理やコンピュータビジョンなど特定の計算タスクに特化したアクセラレータの需要が増大したこと。次に、異なるワークロードに最適化されたプロセッサを組み合わせることで全体の電力効率を向上させるという設計思想が広まったこと。そして、各ハードウェアベンダーが独自のISAやIPコアを開発・販売する閉鎖的なエコシステムが形成されたことである。

RISC-Vはこのような断片化に対する解決策として、「すべての用途で共通して使える、安定した、自由でオープンなISA」というアイデアの生まれた。RISC-Vの最大の強みは、基本ISAに加えて拡張命令セットが体系的に整理されており、様々な用途向けに一貫した方法でカスタマイズできる点にある。ベクトル演算用の「V」拡張、ビット操作用の「B」拡張、浮動小数点演算用の「F/D」拡張など、用途に応じた拡張が整備されている。これにより、汎用CPUからマイクロコントローラ、各種アクセラレータまで、様々な種類のプロセッサを同一のISA体系の下で設計・実装することが可能となる。

実際に、Esperanto TechnologiesのET-SoC-1では、1,000以上のRISC-Vコアを単一チップに集積し、高性能コアから省電力コア、専用アクセラレータまで全てRISC-V命令セットで統一することに成功している。これにより、ソフトウェア開発の複雑性を大幅に削減し、開発効率の向上を実現している。

このように、RISC-Vはヘテロジニアスコンピューティングの時代において「共通言語」としての役割を果たし、異種混合システムの複雑性を低減するという重要な課題を解決しつつある。

ムーアの法則の限界が見え始める中で、オープンで幅広い用途に対応できるこのISAの存在は、今後の技術発展を加速させ、半導体業界全体に大きな影響を与えていくだろう。

まとめ

近年、RISC-Vは急速に普及し始めている。その理由は、以下の2点に集約される:

- 技術的優位性 - x86の複雑なデコード処理やMIPSの遅延分岐など過去のISAの問題を解決し、シンプルで効率的な設計を実現している。

- オープンで柔軟なエコシステム - ライセンス料なしで利用でき、自由に拡張できるオープンソースモデルにより、ヘテロジニアスなSoC設計に最適なプラットフォームとなっている。

現時点では性能面でx86やARMが優位だが、これは40年以上の開発歴史によるものである。わずか10年ほどの歴史しかないRISC-Vは、すでに多くの分野で実用化を実現している。

産業界での採用も急速に拡大している。NVIDIAは次世代GPUコントローラに、GoogleはTitanセキュリティチップに、Western Digitalは全ストレージ製品のコントローラにRISC-Vを採用している。また、Alibabaはクラウドサーバー向け高性能プロセッサを開発し、IntelもFPGAソリューションを提供するなど、業界を代表する企業が次々とRISC-Vを取り入れている。

市場予測によれば、2025年にはRISC-Vチップの出荷数が160億個を突破し、2027年には組み込み市場の25%を占め、2030年にはサーバー市場でも10%のシェアを獲得するとされている。

このように、RISC-Vはオープンソースのアーキテクチャとしての枠を超え、次世代コンピューティングの基盤としての地位を確立しつつある。特に、ヘテロジニアスコンピューティングが主流となる中で「共通言語」としての役割を果たし、AI/ML処理やエッジコンピューティングといった新たな計算パラダイムとの親和性の高さから、今後さらなる成長が期待される。

参考文献

- RISC-V原典 オープンアーキテクチャのススメ

- RISC-V 101. RISC-V Summit

- Wind River - RISC-V Solutions

- RISC-V Market Trends And Predictions Till 2030

- Western Digital to Use RISC-V for Controllers, Processors, Purpose-Built Platforms

- NVIDIA’s Moves to RISC-V!

- What is the Titan M2 security chip in Google’s Pixel phones?

- ET-SoC-1 Chip with More Than 1,000 RISC-V Cores Aimed at Accelerating Machine Learning